Features

- Easily interfaces to the most popular microprocessors.

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from serial data stream.

- Holding and shift registers eliminate the need for precise synchronization between the CPU and the serial data.

- Independently controlled transmit, receive, line status, and data set interrupts.

- Programmable baud generator allows division of any input clock by 1 to (218 — 1) and generates the internal 16 X clock.

- Independent receiver clock input.

- MODEM control functions (CTS, RTS, DSR, DTR, Al, and DCD).

- Fully programmable serial-interface characteristics:

- 5-, 6, 7-, or 8-bit characters

- Even, odd, or no-parity bit generation and detection

- 1-, 1%, or 2-stop bit generation

- Baud Generation (DC to 256 kbaud)

- Complete status reporting capabilities.

- TRI-STATE TTL drive capabilities for bidirectional data bus and control bus.

- Line break generation and detection.

- Internal diagnostic capabilities:

- Loopback controls for communications link fault isolation

- Break, parity, overrun, framing error simulation.

- Fully prioritized interrupt system controls.

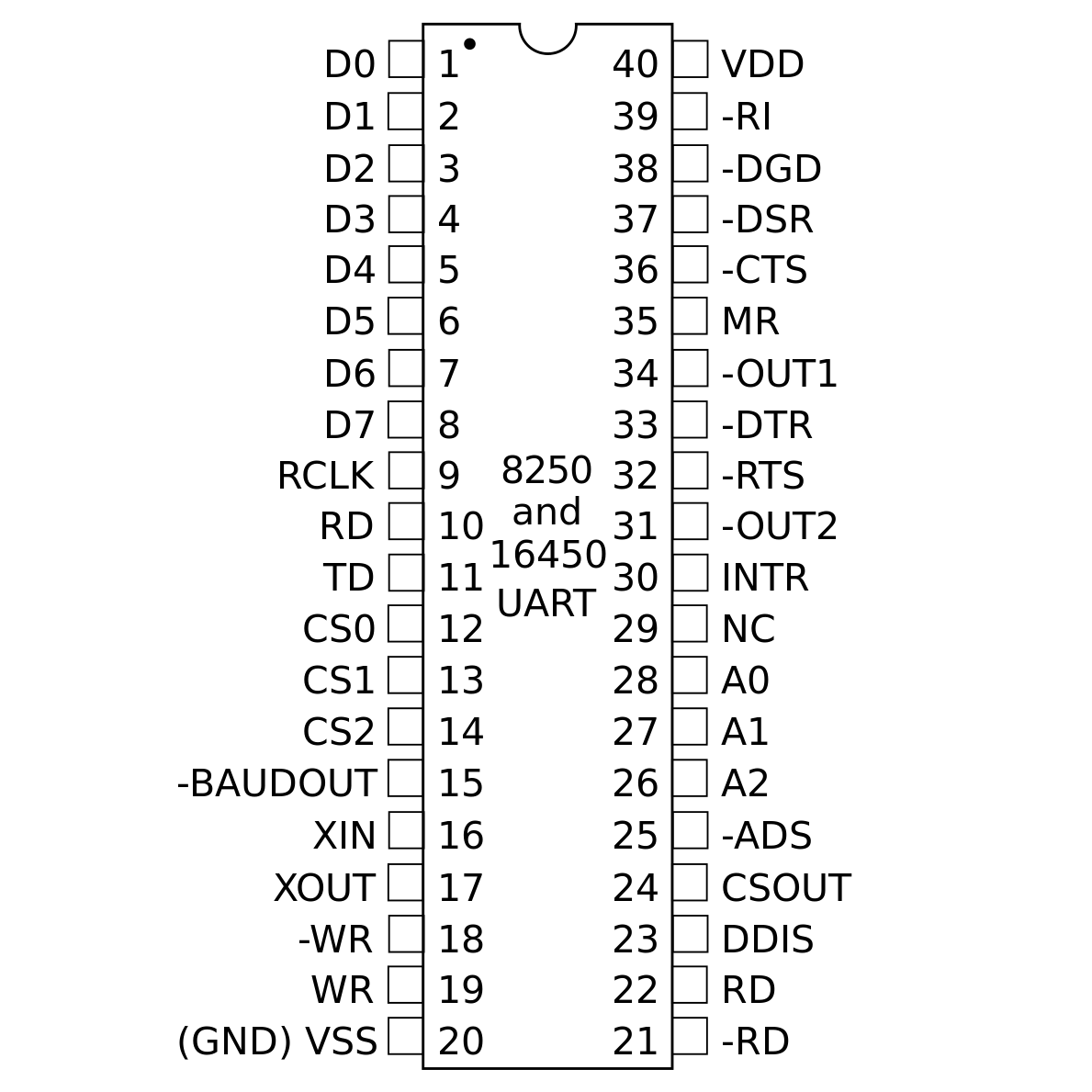

The line interface consists of: SOUT, SIN, /RTS, /DTR, DSR, /DCD, /CTS, /RI

Clock interface: XIN, XOUT, /BAUDOUT, RCLK

Computer interface: D0..D7, /RD, /WR, INTRPT, MR, A0, A1, A2, ADS, WR, RD, /CS2, CS1, CS0

The interrupt line will (when the IER bit has enabled it) be triggered to go high when one of the following events occurs: Receiver line status, Received data available, Transmitter holding register empty, and MODEM status. The interrupt signal is reset to a low level upon the appropriate interrupt service or a reset operation (via MR).